O Trabalho de Arq II deverá ser entregue dia 19/05/2010

Instruções

Entrega no e-mail: andverona@hotmail.com

Archive for the 'Arq. Comp. II 1216/31' Category

Page 3 of 3

Registradores

Encontra-se dentro da CPU, bem próximos as unidades de execução (UA, FPU), apresentando baixo tempo para entregar dados (Baixa latência) trabalham na mesma freqüência da CPU possuem baixa capacidade de armazenamento (em geral 64 ou 128 bits. A maioria dos registradores internos possui o mesmo número de bits do B.D Para armazenamento dos dados são utilizados dispositivos eletrônicos chamados Flip-Flops. Cada Flip-Flops armazena 1 bit. O tempo Médio de acesso a 1 registrador é de 1 nanosegundo.

Memória Cache

Memória interna a CPU responsável pelo armazenamento temporário dos dados que estão sendo utilizados. Principal reponsável pelo desempenho e pelo custo de uma CPU atual. A cache é estruturada em níveis contendo capacidades menores em níveis inferiores.

Exemplo: Intel Core i7 975 => L1: 32+32KB (Por núcleo)

L2: 256 KB (por Núcleo)

L3: 8 MB (Compartilhada)

4 nucleos fisicos,

AMD PHENONII 965=> L1: 64+64KB (por núcleo)

L2: 512 KB(por núcleo)

L3: 6 MB (Compartilhada)

Memória Principal

Memória localizada na placa-mãe com velocidade inferior a cache. Trabalha com frequências inferiores a cada CPU

Valores Atuais:

1GB, 2GB e 4 GB ( por pente)

800, 1066, 1333, 1600 MHZ

Obs: Memórias gráficas =>4000 MHZ

Tempo de acesso: 50 a 80 Nanoseg.

Utiliza capacitores para armazenamento dos dados (1 por bit). Com a carga dos capacitores se perde com o tempo é necessario um recarregamento periódico, chamado refresh.

Um pente típico possui 64 bits de largura.

Algumas placas de vídeo podem atingir até 892 bits de largura nas suas memórias.

Exemplo: Taxa Transferência memória i7 975 = DDR 1333

Tripple channel

3 * 1333 * 64 bits

NVIDIA GXT295 2200 * 892 Bits = 32GB/s

Discos e CD ROMs

Não voláteis. Utilizam meios ópticos e magnéticos para armazenar dados.

Prova 1º bim 04/05/2010

Aula 07

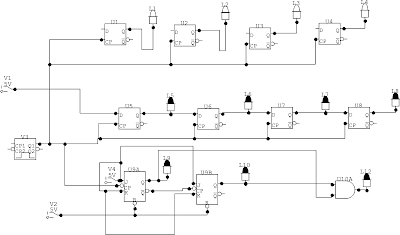

Utilizando o Circuit maker ou KtechLab

- Implementar um conversor serial/paralelo

- Implementar um conversor paralelo/serial

- Analisar formar implementar um sistema com barramento de dados de endereços e de controle (Semelhante ao trabalho)

- Entrada Chaves, Buffer 3s, Registradores 2 3 4 , Pino de controle, seletor de endereços

- Controle 0: Leitura 1:Escrita

A Aula 08 (20/04/2010) será no laboratório DIN

Tópico de Aula 07:

- Transmissão de dados Serial: Serial e Paralelo

- Barramento Serial

- Transmissão Serial

- Transmissão Serial Assíncrona (UART)

- Transmissão Serial Síncrona

- Transmissão Paralela

Foi passado exercícios sobre barramentos

(Obs.: Irei disponibilizar scan do carderno se houver >=1 pedidos nos comentários)

Material interessante para estudo:

Arquitetura do Processador 8085 – UNESP

AULA 04 – 23/03/2010

Barramentos

Referencias:

Conceitos Basicos – Barramento [PDF]

Barramentos 01 [PDF]

Barramentos e Estrutura de Interconexões (Clube do Hardware) [PDF]

AULA 03

- Conceitos Básicos da Arquitetura de Computadores

Twitter

Twitter